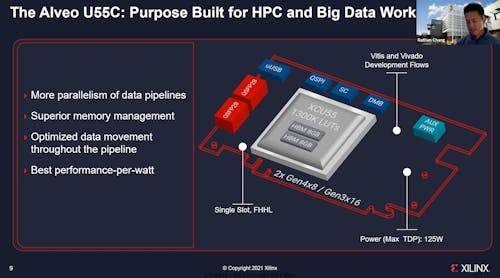

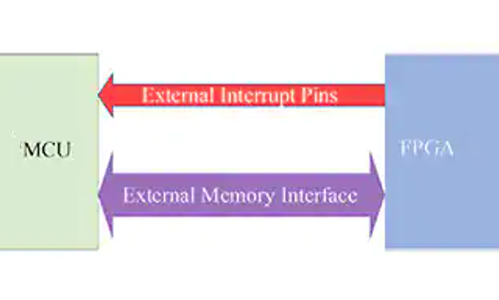

The new line of Agilex FPGAs developed byIntel提供令人印象深刻的功能,包括对新的支持Compute Express Link (CXL)standard design that puts devices on an equal footing with host processors. The family takes advantage of the company’s die-to-die interconnect,嵌入式多-DIE互连桥(EMIB),最初是由Altera开发的,现在是英特尔的一部分。EMIB允许英特尔将EMIB连接的芯片或瓷砖与对高速收发器,PCI Express(PCIE)和SOC版本的四核ARM Cortex-A53复合物混合使用。(Fig. 1)。

1.Agilex FPGA使用EMIB连接混合its FPGA fabric with other devices, including processors, high-speed interfaces, and memory.

The Agilex is based on Intel’s 10-nm technology. It provides a 40% performance boost compared to the Intel Stratix 10 while reducing power by up to 40%. The top-end systems can deliver up to 40 TFLOPS (FP16 performance) using the new DSP blocks, and are designed to handle DDR5 and provide on-chip high bandwidth memory (HBM) along with support for off-chip Intel Optane DC persistent memory. The top end will also support 112-Gb/s transceivers as well as PCI Express Gen 5.

The EMIB support is used to provide connections from the FPGA fabric to these interfaces, but it can also be used for custom tiles. Intel’s eASIC effort will allow companies to incorporate their tiles into custom Agilex FPGAs(Fig. 2)。EASIC是一种Agilex FPGA,使用EMIB链接到系统的客户供应瓷砖。这为FPGA提供了ASIC的许多优势,但启动成本的灵活性。该方法可用于将许多芯片集成到一个可配置的平台中。

2. Intel’s eASIC provides a bridge between FPGA solutions and custom ASICs.

CXL支持(Fig. 3)是英特尔FPGA的主要进步之一。尽管它需要在主机处理器中进行匹配的支持,但它提供了一种常见的缓存,可加速的内存体系结构,该内存体系结构是在PCI PCIE上构建的。从本质上讲,它将所有CXL设备都放在同一级别上,从而使FGPA可以访问共享内存和外围设备。

3. Agilex supports the new Compute Express Link (CXL) standard for linking devices to host processors in a cache-coherent way.

CXL is a new platform and Agilex will be one of the first out there to include it. Intel will have matching support in a future Xeon family, at which point CXL becomes very interesting. From a programming point of view, there’s no difference between a processor and an FPGA working on the data in shared memory. It’s even possible that one instance of an application will use processor-based support while another employs an FPGA implementation. The operating system could transparently utilize what’s needed or available at the time.

Intel FPGAs are already used in the data center in theProgrammable Acceleration Cards (PACs),使用PCIE接口。CXL还建立在PCIE上,但由于缓存的性质,它提供了较低的文献实现。

In addition, the Agilex FGPA fabric has been updated and optimized to handle new applications such as deep neural networks (DNNs) used in machine-learning (ML) applications. The configurable DSP now supports FP32, BFLOAT16, FP16, as well as INT8 through INT2. These are numeric formats being using in ML applications. It allows the DNN models to be optimized at each stage in an FPGA implementation without the overhead of using the FPGA fabric for all of the computation. The DSP block handles it more efficiently as long as it maps to the algorithm. Frameworks like the OpenVINO inference system for vision can take advantage of this accelerated hardware support.

Agilex家族有多种版本(Fig. 4)。The first one available is the F-Series, which has 58-Gb/s transceivers, PCIe Gen 4 support, DDR4 memory controllers, and an optional quad-core, 64-bit, Arm Cortex-A53 compute complex. The I-Series and M-Series kick the transceiver speed up to 112 Gb/s and support PCIe Gen 5. This is also where the CXL support comes into play. The M-Series is designed for compute-intensive applications. It adds support for DDR5 and Intel Optane DC. Furthermore, an HBM option puts large amounts of storage onto the system.

4. Agilex F系列将首先提供。I系列和M系列添加了CXL支持,而M系列则具有HBM支持。

Agilex版本与新的开发人员支持一致。石英素数设计工具通过新的工作流提供了更高的生产率,并提高了30%的工作编译时间。这些工具还具有15%的内存利用率。这些工具包括英特尔的VTUNE放大器和英特尔顾问支持。该工具集处理所有英特尔FPGA,包括新的Agilex。

Intel expects the Agilex to be used in everything from 5G to data centers to embedded avionics.